Построение процессорной системы на базе ARM-процессора

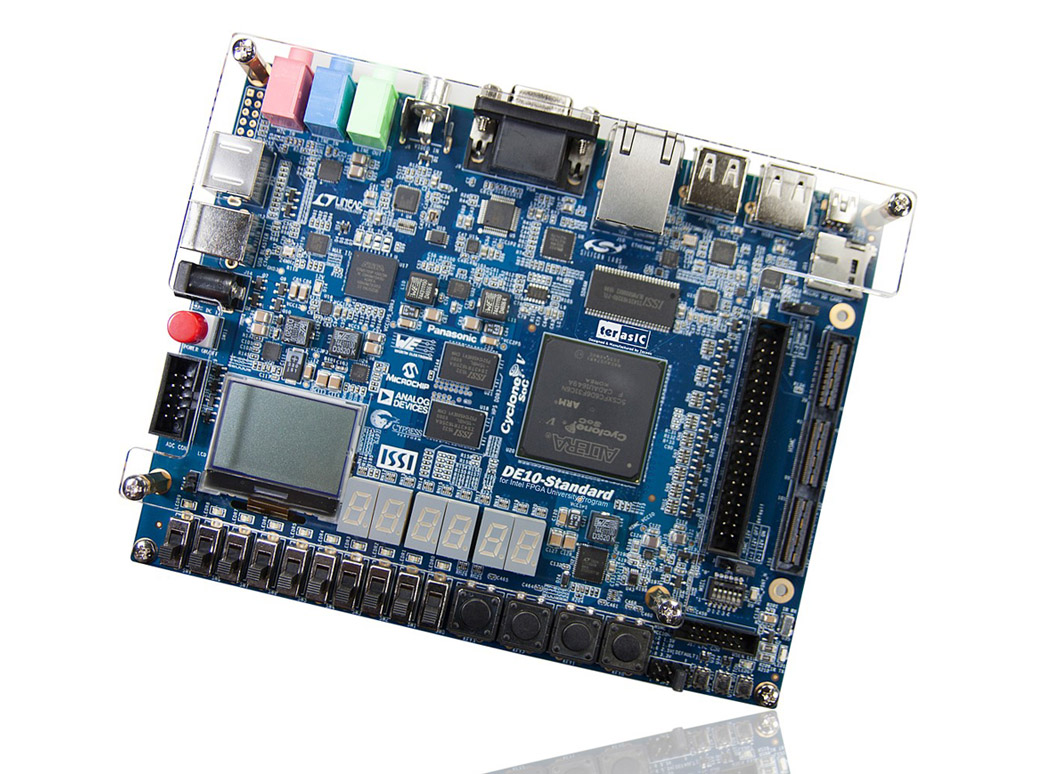

Программа «Построение процессорной системы на базе ARM-процессора» разработана с целью формирования у слушателя знаний и навыков построения процессорной системы на базе ARM-процессора на SoC фирмы Intel FPGA (ранее Altera). В курсе рассматривается инструмент Platform Designer (ранее QSYS), входящий в среду проектирования Quartus Prime, структура Hard Processor System (HPS), принципы построения проекта на базе HPS и основы разработки программного обеспечения для HPS в программе ARM DS-5. Для инженеров, которые уже работают с ПЛИС, курс позволяет изучить новое направление по работе с системами на кристалле (SoC) в САПР Quartus Prime и ARM DS-5.

| Продолжительность обучения | 4 дня | |

| Место проведения | Санкт-Петербург, Новоизмайловский проспект, 34к3 | |

| Форма обучения | с 10:00 до 17:00 | |

| Стоимость обучения | ~76000 руб * | |

| Контакты | +7(962)722-36-80 / cpe.ifmo@yandex.ru |

Цель курса:

Дать необходимые начальные знания и навыки для работы с процессорной системой на базе ARM-процессора на SoC фирмы Intel FPGA в среде Quartus Prime.

Учебный план

| Тема | Всего часов* | Лекции* | Практика* |

|---|---|---|---|

| Инструмент Platform Designer (инструмент системной интеграции) | 3 | 1 | 2 |

| Интерфейс AXI | 4 | 2 | 2 |

| Структура HPS | 4 | 3 | 1 |

| Конфигурация HPS-системы | 3 | 1 | 2 |

| Разработка программного обеспечения для HPS | 7 | 2 | 5 |

| Процесс загрузки системы | 3 | 1 | 2 |

| Взаимодействие между FPGA и HPS | 4 | 2 | 2 |

| Отладка HPS | 3 | 1 | 2 |

Необходимые знания:

- знание основ цифровой схемотехники

- знание тем курса Основы проектирования на FPGA

- знание основ программирования на языке C/C++

Программа курса

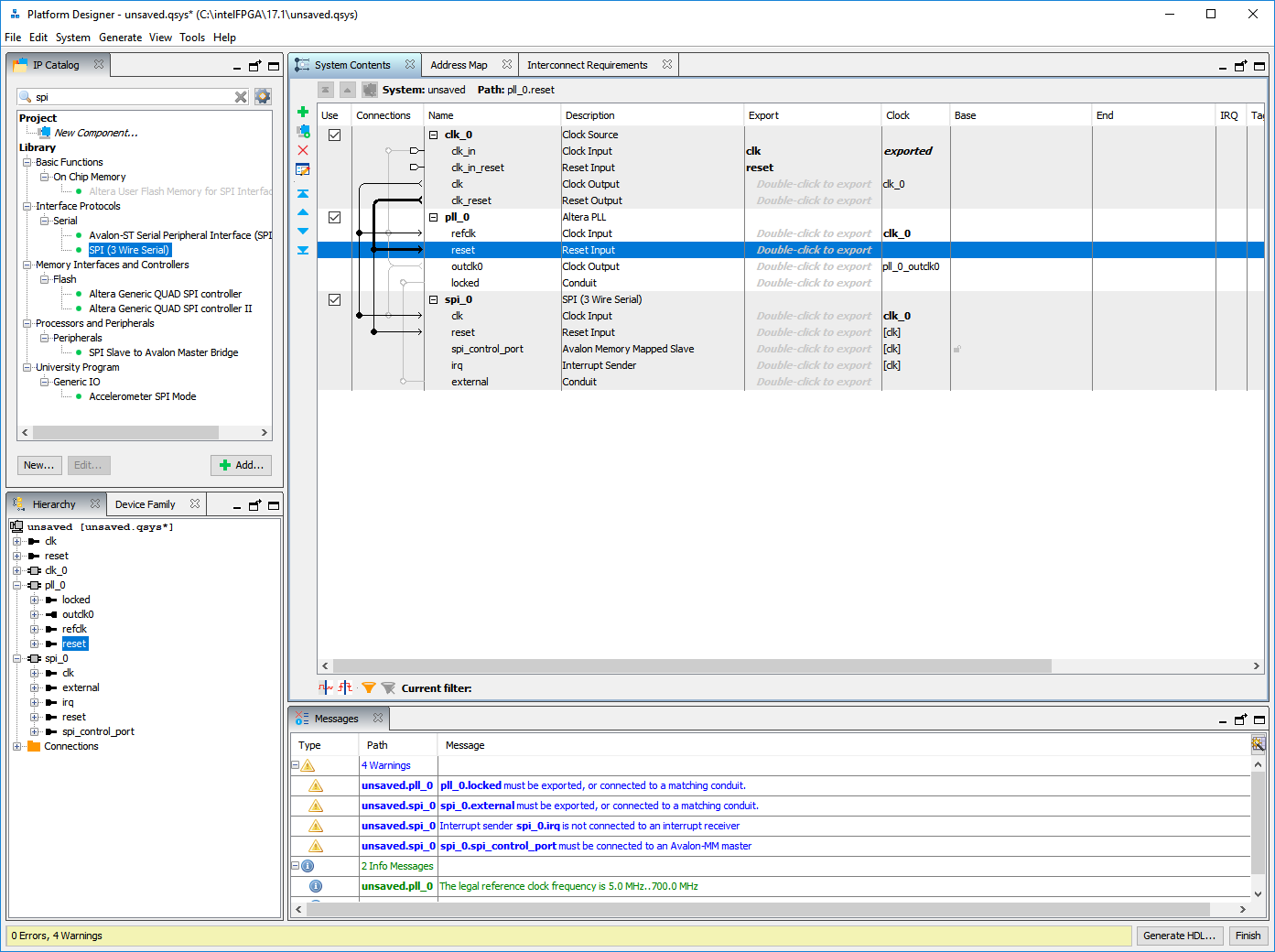

| Тема 1 Инструмент Platform Designer (инструмент системной интеграции) |

Демонстрируется инструмент Platform Designer, на практике рассматриваются принципы построения систем в Platform Designer и методы интеграции их в дизайн. |

| Тема 2 Интерфейс AXI |

Рассматриваются виды интерфейсов AXI и их различия. Рассказывается, какие инструменты для использования AXI интерфейсов присутствуют в Quartus Prime и как, используя их, строить систему. |

| Тема 3 Структура HPS |

Подробно рассматривается архитектура процессора ARM Cortex A9 и структура HPS. |

| Тема 4 Конфигурация HPS-системы |

Демонстрируется как настроить HPS-систему в Platform Designer, как задействовать необходимые элементы архитектуры и как интегрировать ее в FPGA-дизайн. |

| Тема 5 Разработка программного обеспечения для HPS |

Демонстрируется инструмент ARM DS-5. Рассказывается о составе конфигурационных файлов, автоматически сгенерированных компонентах и HAL. Рассматриваются методы написания программного обеспечения для HPS. |

| Тема 6 Процесс загрузки системы |

Подробно рассматривается процесс загрузки системы, рассказывается о способах сборки и модификации U-boot и Preloader. |

| Тема 7 Взаимодействие между FPGA и HPS |

Рассказывается о способах обмена данными между FPGA и HPS. Подробно рассматриваются имеющиеся интерфейсы и способы их использования как со стороны HPS, так и со стороны FPGA. |

| Тема 8 Отладка HPS |

Показываются примеры отладки HPS. Демонстрируется cross-triggering – инструмент отладки двустороннего взаимодействия между FPGA и HPS. |